TSMC задумалась о строительстве в Японии предприятия по тестированию и упаковке чипов

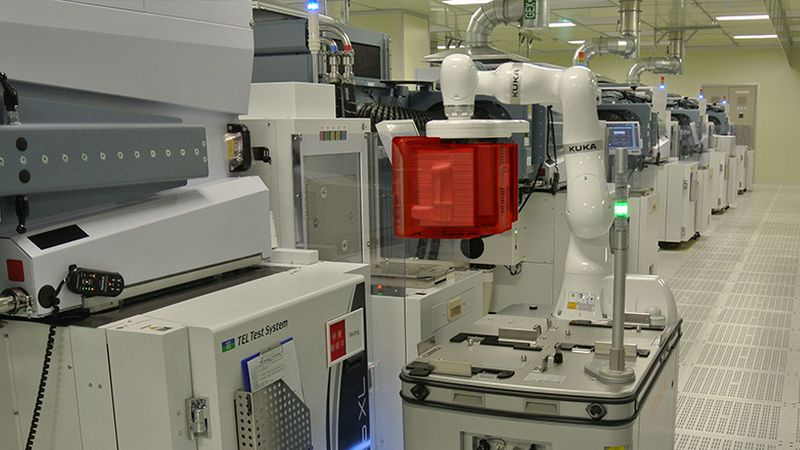

Давно известно, что одна из причин существующего дефицита передовых ускорителей вычислений — это ограниченные возможности TSMC по тестированию и упаковке чипов для них с использованием технологии CoWoS. Все профильные мощности компании сосредоточены на Тайване, но теперь Reuters сообщает о наличии у TSMC намерений построить подобное предприятие в Японии.

Напомним, что в Японии TSMC уже реализует проекты по строительству двух предприятий, обрабатывающих кремниевые пластины с использованием относительно зрелой по тайваньским меркам литографии, а её исследовательский центр по использованию различных перспективных материалов и методов упаковки чипов в большей мере ориентирован на интересы самой TSMC, а не японских партнёров из числа поставщиков материалов и технологического оборудования.

Предприятие по упаковке чипов с использованием методики CoWoS, скорее всего, пригодилось бы кому-то из производителей чипов на территории Японии, который использует передовую литографию. В этом контексте главным бенефициаром данной инициативы кажется японский консорциум Rapidus, который уже в 2027 году надеется начать выпуск в Японии передовых 2-нм чипов. Впрочем, пока нет точной информации ни о сроках строительства обсуждаемого предприятия TSMC по упаковке чипов, ни о бюджете такого проекта. В настоящий момент основная часть клиентов TSMC, нуждающихся в услугах по упаковке чипов по методу CoWoS — это американские компании, как поясняют эксперты TrendForce.

Кстати, Intel и Samsung тоже собираются использовать компетенции японских производителей оборудования и поставщиков расходных материалов в своих интересах. Первая изучает возможность строительства в Японии профильного исследовательского центра, а вторая уже достигла соответствующей договорённости с местными партнёрами. Напомним, что у TSMC такой исследовательский центр на территории Японии уже есть.